- Produkt wycofany

|

Uwaga! Sprzedaż produktu została zakończona. Sprawdź inne w tej kategorii. |

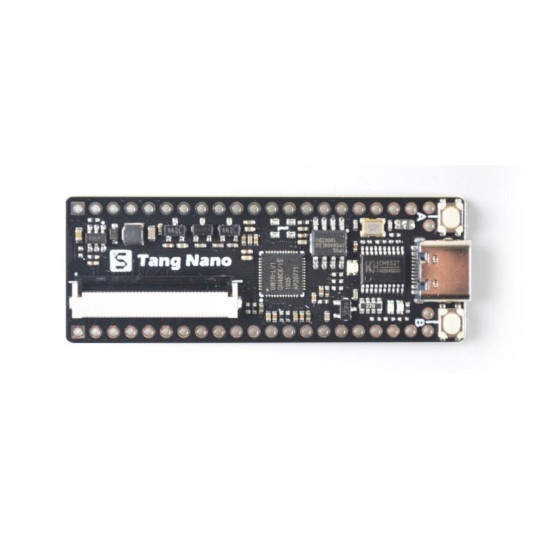

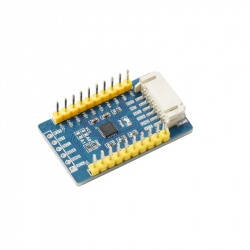

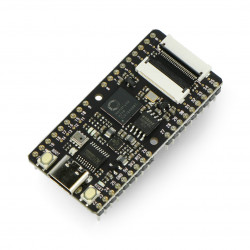

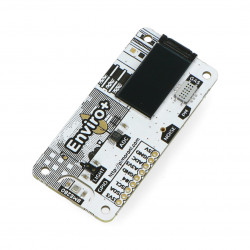

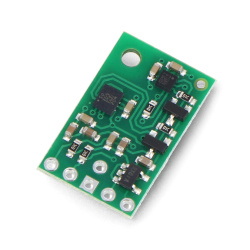

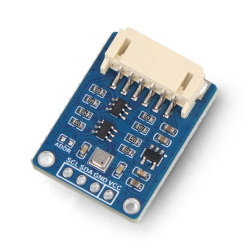

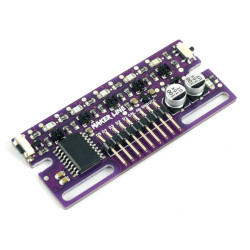

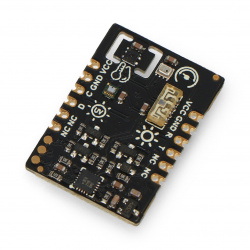

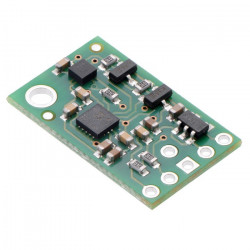

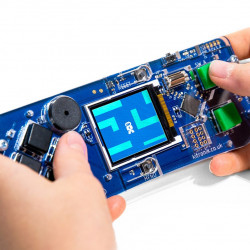

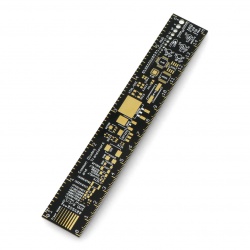

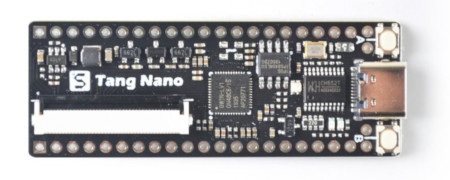

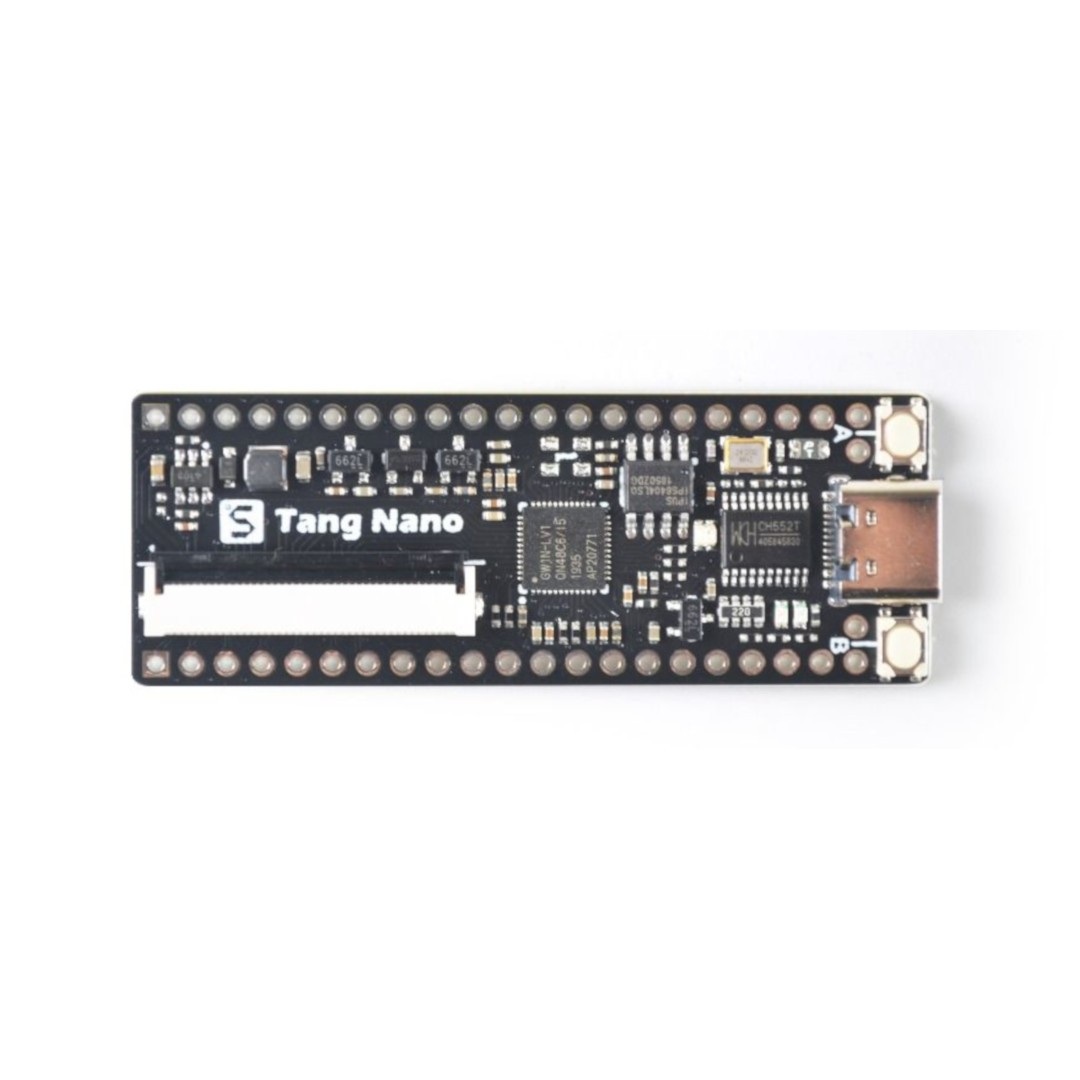

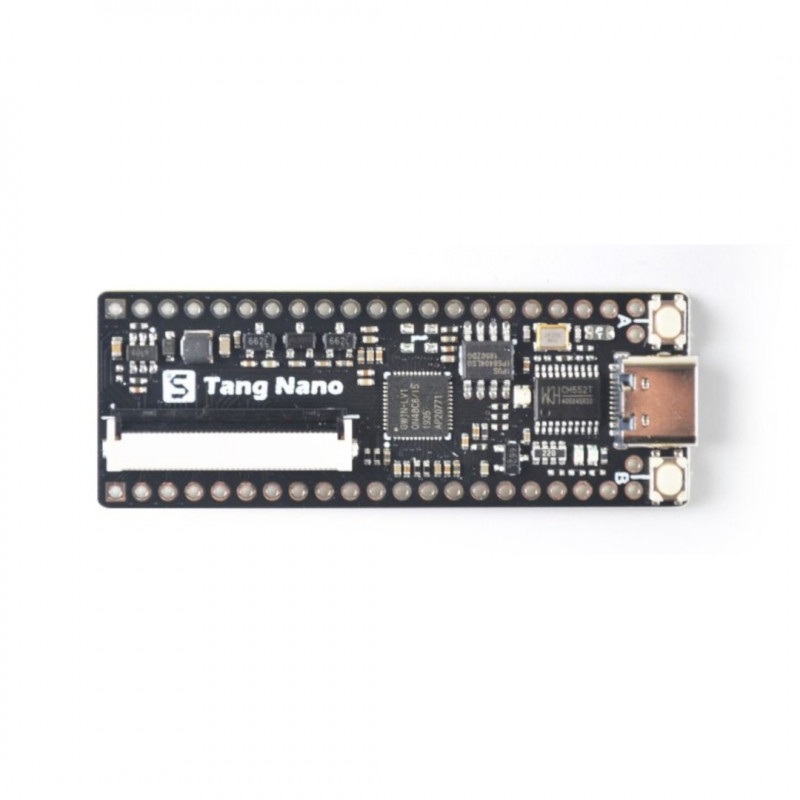

Opis produktu: Sipeed Tang Nano - płytka rozwojowa FPGA GW1N-1

Płytka rozwojowa oparta o układ GW1N-1-LV, który posiada 1152 LUT4 z 4 adresami RAM oraz 864 FF (Flip-Flop). Moduł posiada 72 kb pamięci SRAM. Z powodu niewielkich rozmiarów płytka nie posiada modułu DSP, przez co nie można wykonać złożonych obliczeń, takich jak akumulacja. Została wyposażona w 34 piny I/O. Płytka zasilana przez złącze USB C. Sipeed Tango Nano programowany jest przez interfejs JTAG z wykorzystaniem USB, bez konieczności używania dodatkowego downloadera. Wbudowane złącze FPC 40-pin umożliwia podłączenie wyświetlacza.

Główne cechy płytki Sipeed Tango Nano

- Układ: GW1N-1-LV z 1152 LUT4 oraz 864 FF

- 72 kb pamięci SRAM, 96 kb pamięci flash

- Złącze FPC 40-pin do podłączenie wyświetlacza

- Wbudowany downloader JTAG

- Nie wspiera DSP

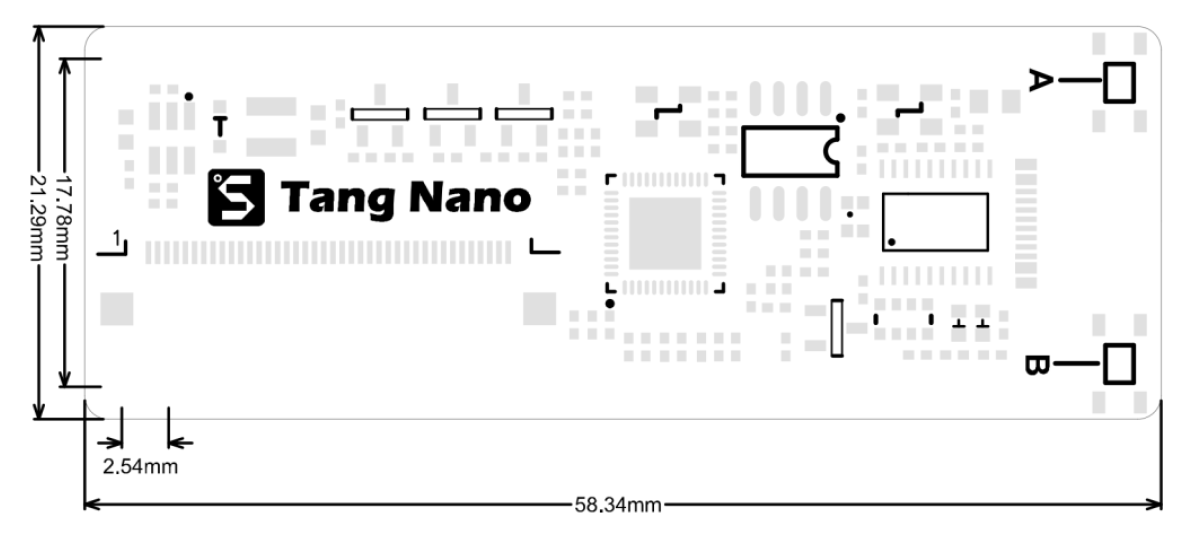

- Niewielkie rozmiary: 58,34 x 21,29 mm

Specyfikacja płytki Sipeed Tang Nano

- Układ: GWIN-1-LV:

- LUT4: 1152

- Flip-Flop: 864

- SRAM: 72 kb

- Flash: 96 kb

- PLLs+DLS 1+0

- Napięcie rdzenia: 1,2 V

- Programowanie: USB

- Zasilanie: 5 V - USB C

- Pobór prądu: do 400 mA

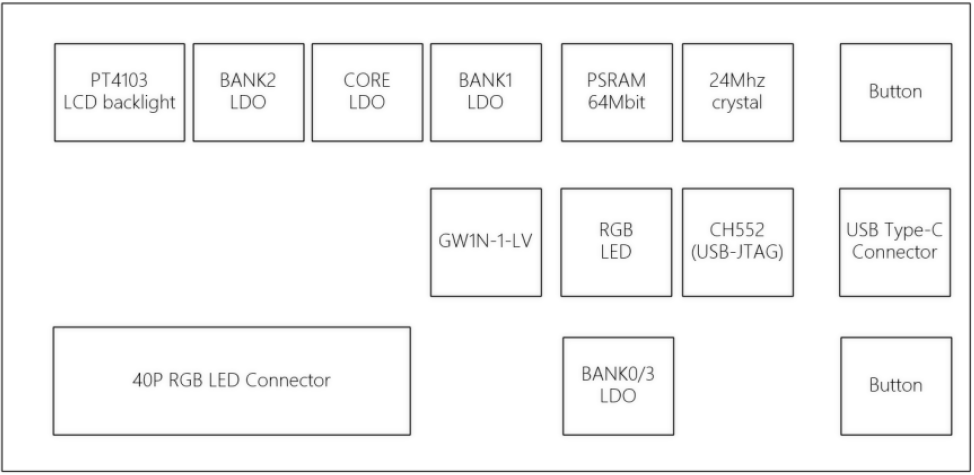

- Obwód zasilania: każdy Bank posiada osobny układ zasilania LDO (z wyjątkiem BANK0/3). Poziom I/O w BANK 1 i BANK2 można dostosować zmieniając układ LDO

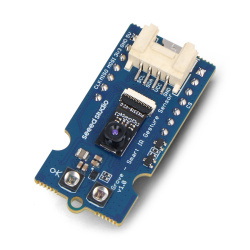

- Wyświetlacz: 40-pin FPC - wbudowany sterownik podświetlenia wyświetlacza

- I/O: 32-pin

- Pamięć PSRAM: 64 Mb 3,3 V

- Diody: wbudowane diody LED RGB

- Przycisk: 2 przyciski 3 x 4 mm

- Kwarc: wbudowany oscylator kwarcowy 24 MHz

- Temperatura pracy: od -30°C do 50°C

- Wymiary: 58,34 x 21,29 mm