Spis treści:

Jeśli spytać by kogoś, kto zajmuje się elektroniką, jak wygląda tranzystor? Odpowiedź brzmiałaby pewnie – zwyczajnie, niewielki element w hermetycznej obudowie z trzema wyprowadzeniami. Ci nieco kreatywniejsi mogliby powiedzieć, że obudowy tranzystorów bywają różne i zależnie od ich mocy są one większe lub mniejsze. Odpowiedź ta jest jak najbardziej poprawna, wszakże tak właśnie wygląda tranzystor, jest to element elektroniczny z trzema wyprowadzeniami. Zastanówmy się jednak czy na pewno?

Jak głosi przysłowie, diabeł tkwi w szczegółach i to jak wygląda tranzystor, można w dość prosty sposób rozwinąć. Możemy zastanowić się, czym tak naprawdę w gruncie rzeczy jest tranzystor, czy jest to element elektroniczny jako całość, czy też może tylko jego rdzeń. Mówimy przecież, że w układach scalonych również znajdują się tranzystory, ale na próżno szukać w najnowszym procesorze Intela tych „klasycznych” tranzystorów.

Wszystko zależy od punktu widzenia, w zwyczajnym pojedynczym tranzystorze, struktura krzemowa umieszczona wewnątrz będzie jego rdzeniem, ale w układzie scalonym, a dokładniej w jego rdzeniu, również znajdziemy tranzystory, tyle tylko, że umieszczone we większym kawałku krzemu, który skrywa też inne tajemnice.

Na przestrzeni lat, klasyczne tranzystory montowane początkowo w procesie przewlekanym THT, a później powierzchniowym SMD przechodziły różne modyfikacje. Zmieniały się rodzaje obudów, raster wyprowadzeń, ale sam rdzeń pozostawał z grubsza taki sam. Oczywiście on również z biegiem lat podlegał stopniowej miniaturyzacji, ale konstrukcyjnie był taki sam. Sprawa ta, wygląd jednak nieco inaczej w przypadku układów scalonych.

Układy scalone również ewoluowały, można powiedzieć, że nawet znacznie bardziej niż tranzystory, ponieważ nie zmieniał się tylko ich fizyczne wymiary, czy też sposób montażu, ale najważniejszą kwestią była tutaj ewolucja krzemowych struktur. Jest to jednak temat bardzo obszerny, który znacznie wykracza poza obszar niewielkiego internetowego artykułu. Dlatego zajmiemy się tylko małym skrawkiem krzemowej ewolucji, a dokładniej sposobem budowy tranzystorów w układach scalonych.

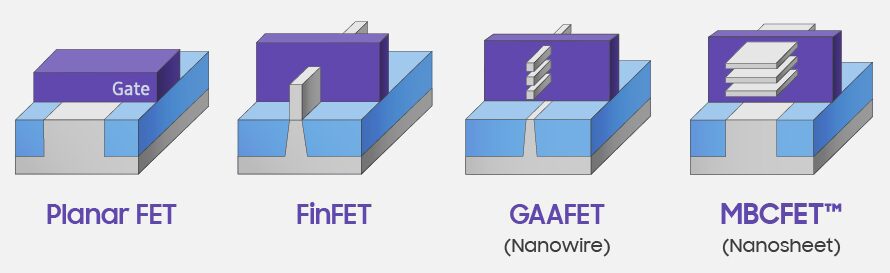

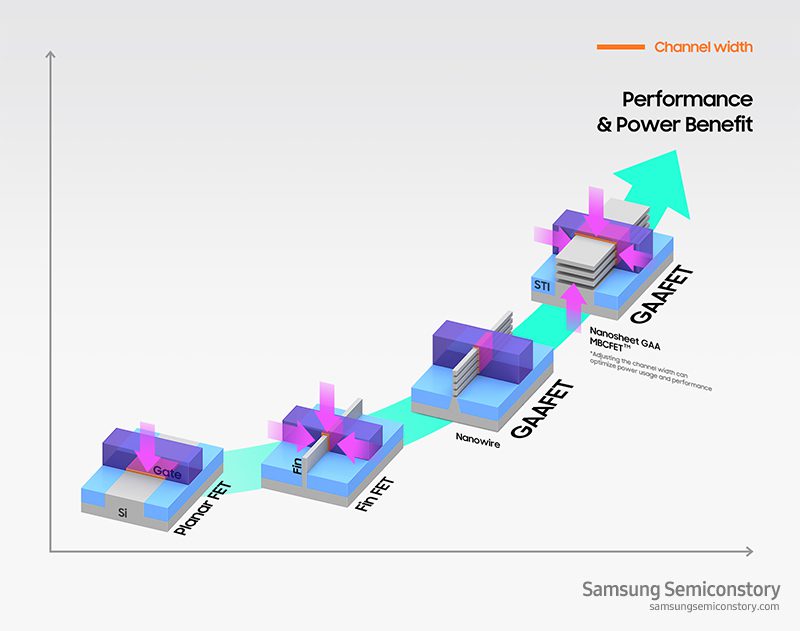

Tych na przestrzeni lat było kilka. Wszystko zaczyna się od tranzystorów typu Planar FET, te stosowano niemal od czasu powstania pierwszych układów scalonych do pierwszej dekady lat 2000., co trzeba przyznać, jest dość sporym okresem czasu. Świadkami pierwszej rewolucji krzemowej byliśmy w okolicach 2011 roku. To wówczas na rynku zaczęła dominować technologia FinFET, stosowana z powodzeniem po dziś dzień. Jednak postępująca miniaturyzacja, potrzeba coraz większej mocy obliczeniowej motywowana rozwojem sztucznej inteligencji, czy też próby zoptymalizowania zapotrzebowania na moc współczesnych układów scalonych wymogła na konstruktorach kolejne zmiany. Ich efektem są tranzystory GAAFET, dopiero wkraczające na salony, choć na horyzoncie zarysowuje się wizja kolejnej modyfikacji, czyli MBCFET.

Klasyczne tranzystory – Planar FET

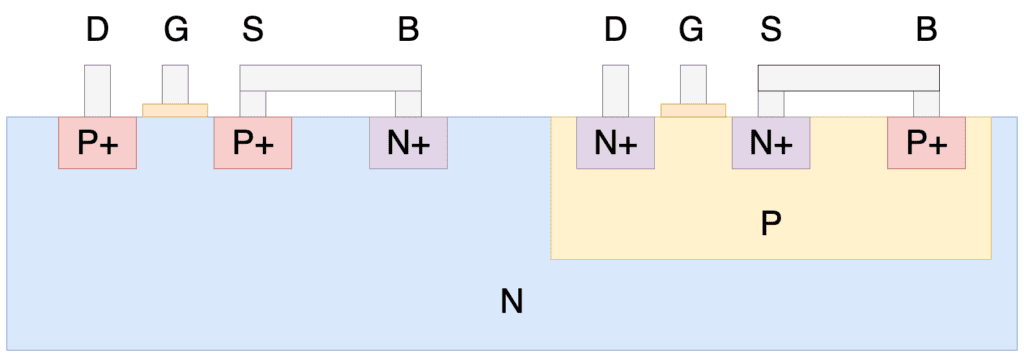

Tranzystory typu Planar FET stosowane były przez dziesięciolecia, stając się tym samym najbardziej podstawową formą tego rodzaju elementów w układach scalonych. W swojej konstrukcji tranzystor ten nie jest niczym skomplikowanym. Na grafice powyżej możecie zobaczyć dwóch przedstawicieli tej technologii, z kanałem typu N i typu P. Obie konstrukcje są do siebie bliźniacze i bazują na tej samej zasadzie działania, różnią się tylko typem domieszki półprzewodnika. W tranzystorach tych wysterowywana odpowiednim napięciem baza tworzy kanał między dwoma obszarami drenu i źródła. Jest on efektem działania pola elektrycznego i to właśnie tędy przepływa prąd elektryczny.

Na grafice zauważyć można jeszcze tajemnicze wyprowadzenie oznaczone jako B, połączone ze źródłem tranzystora. Jest ono niezbędne do poprawnego funkcjonowania tego typu elementów, umieszczonych na krzemowym podłożu. Wymagają one, aby miejsce, w którym znajduje się tranzystor, spolaryzowane było napięciem ze źródła. Dzięki temu sygnały przełączane przez tranzystor, przepływający przez niego prąd, nie może „uciec”. Innymi słowy, wokół tranzystora powstaje bańka, dzięki której jest on niejako odizolowany od reszty krzemowych elementów umieszczonych na tym samym podłożu.

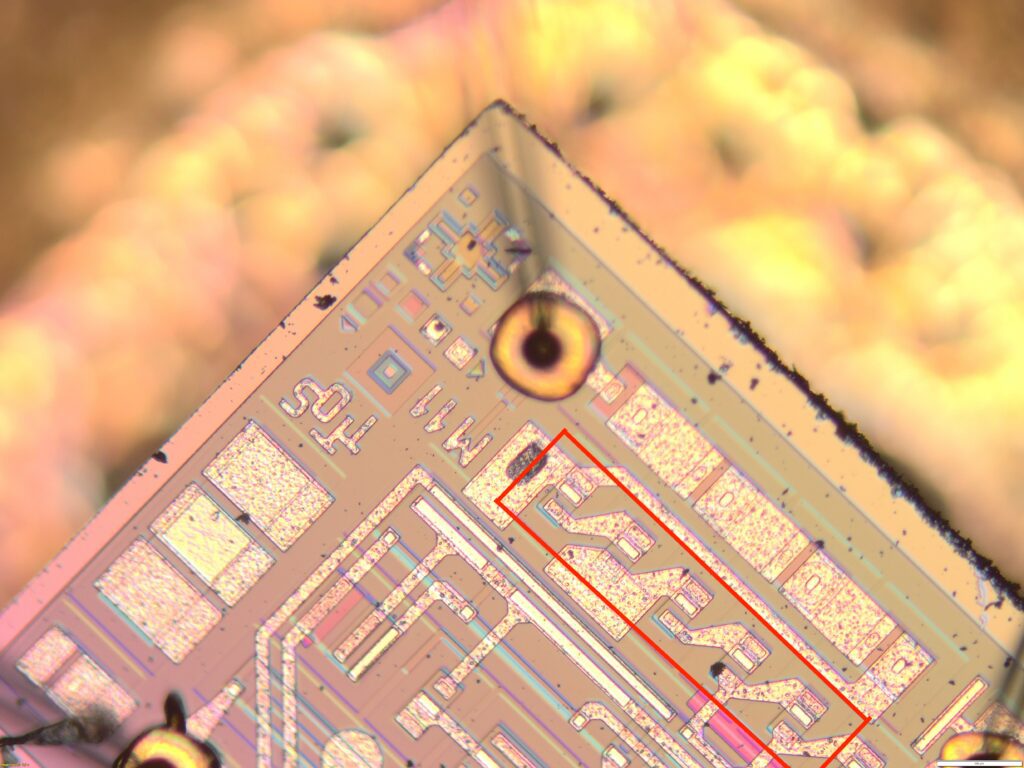

Tranzystory wykonane w opisany wyżej sposób to bardzo uniwersalne konstrukcje, do tego stopnia uniwersalne, że budowano z nich również zwyczajne diody, choć wydaje się, że są to mniej skomplikowane elementy złożone tylko z dwóch warstw półprzewodnika. Jednak w rzeczywistości łatwiejsze okazuje się połączenie bramki i drenu lub źródła zależnie od typu kanału i stworzenie diody w ten sposób. Na fotografii powyżej w zaznaczonym prostokącie możecie zobaczyć właśnie taką sytuację – szereg połączonych ze sobą diod w układzie wiekowej już przetwornicy UL1520 produkcji Warszawskich zakładów CEMI.

Prostota, niskie koszty produkcji, stabilność i przewidywalność działania sprawiły, że tranzystory Planar FET, stały się fundamentem współczesnej elektroniki. Jednak czas każdej technologii mija i tak też stało się, gdy chipy zaczęły osiągać poziom około 28nm. Ciągłe zmniejszanie się tranzystorów sprawiło, że pojawił się efekt tak zwanego, krótkiego kanału. Powodował on problemy w kontrolowaniu przepływającego prądu, czego efektem potrafiło być niepoprawne działanie tranzystora, mimo poprawnie spolaryzowanej bramki.

Pierwsza rewolucja krzemowa – FinFET

Pierwsza tranzystorowa rewolucja, która zdetronizowała konstrukcje typu Planar FET, miała miejsce w okolicach 2011 roku. To wówczas firma Intel ogłosiła światu powstanie pierwszej linii technologicznej dla układów wykonanych w procesie 22nm korzystających z FinFET. Były nimi procesory niebieskich z serii Ivy Bridge zaprezentowane rok później. Warto jednak wiedzieć, że prace nad technologią FinFET rozpoczęto znacznie wcześniej. Już w 1989 roku koncepcja ta zaprezentowana została przez zespół z Hitachi Central Research Laboratory. Digh Hisamoto, Toru Kaga, Yoshifumi Kawamoto i Eiji Takeda pochwalili się wówczas tranzystorem „DELTA”, protoplastom późniejszego FinFET.

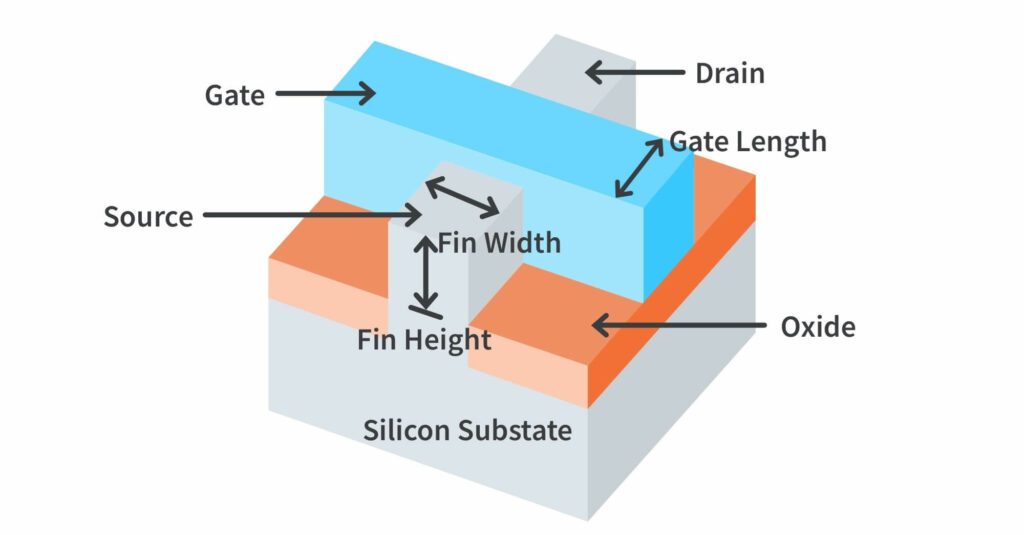

Pomysł jak to zwykle bywa w świecie technologii, był genialny w swej prostocie. Skoro klasyczne tranzystory mogą mieć problem ze zbyt wąskim kanałem – zwiększmy go, ale nie w poziome, a w górę. Podejście to było na swój sposób rewolucyjne. Dotychczas budowa tranzystorów była niejako „płaska” i tworzyły go domieszkowane obszary na jednym poziomie półprzewodnikowego podłoża. Konstrukcje FinFET zrywały z tą zasadą, postanowiono wyciągnąć część podłoża w górę, tak aby stworzyć obszar otoczony z trzech stron przez bramkę. Krzemowe tranzystory otrzymały dodatkowy wymiar – wysokość.

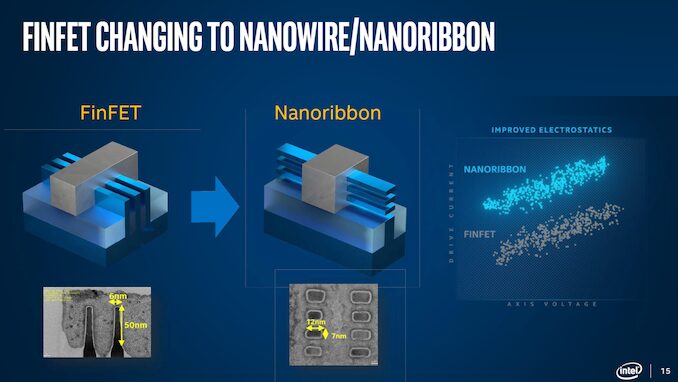

Graficzną reprezentację konstrukcji FinFET możecie zobaczyć na grafice powyżej. Jak widać, jest to zasadniczo ten sam tranzystor co wcześniej, tylko z dodatkową „płetwą”, stąd też wzięła się jego nazwa „Fin”. W poprzedniej generacji elementów kanał, którym przepływały nośniki ładunku, powstawał w okolicach bramki, która stykała się z półprzewodnikiem tylko w krótkiej przestrzeni między drenem a źródłem. Stąd też wynikał problem zbyt wąskiego kanału, im mniejsze były tranzystory, tym trudniej było kontrolować tak mały obszar. W rozwiązaniu FinFET bramka łączy się z półprzewodnikiem w trzech miejscach, na trzech ściankach „płetwy”. W ten sposób, po podaniu odpowiedniej wartości napięcia na bramkę, tworzy się kanał na niemal całej powierzchni wyciągniętego w górę obszaru, rozwiązując problem tranzystora Planar FET.

Technologia FinFET, mimo że przełomowa nie piastowała stanowiska króla budowy półprzewodnikowych tranzystorów zbyt długo, zwłaszcza jeśli spojrzymy na całą historię elektroniki. Problemy zaczęły się pojawiać mniej więcej w 2020 roku, gdy fabryki półprzewodników na szeroką skalę zaczęły wytwarzać chipy w rozmiarze 5nm. Tutaj również winna okazała się miniaturyzacja. Mniejszy tranzystor, oznaczał mniejszą „płetwę” a to skutkowało ograniczeniami w przepływie prądu. Tak jak przekrój przewodu w domowej instalacji może okazać się zbyt mały do wartości pobieranej energii, tak tym razem okazało się, że zbyt małe są kanały tranzystorów. Poza tym FinFET miewał problemy z tak zwanym efektem „parasitic capacitance”, czyli pasożytniczej pojemności pojawiającej się przy zbyt dużym zagęszczeniu tranzystorów. Gęstość upakowania ujawniała też kolejny problem, czyli odprowadzanie ciepła, dlatego też technologia oczekiwała kolejnej rewolucji.

Druga rewolucja krzemowa – GAAFET

GAAFET (Gate-All-Around Field Effect Transistor) to kolejny krok w ewolucji tranzystorów. Jak wynika z angielskiego rozwinięcia samego skrótu, tym razem bramka otaczać będzie kanał, przez który przepływać będzie prąd ze wszystkich czterech stron. Co więcej, w tej technologii, kanałów może być kilka, co eliminuje problemy przepustowości znany z FinFET.

Co ciekawe pomysł na GAAFET podobnie jak dekadę temu nie jest niczym nowym. Pierwsze koncepcje tego typu tranzystorów powstały mniej więcej w tym samym czasie co pierwsze szkice FinFET. Pod koniec lat 80. XX wieku zespół badawczy z Toshiby w składzie Fujio Masuoka, Hiroshi Takato oraz Kazumasa Sunouchi zaprezentowali światu pierwszy prototyp tranzystora, w którym bramka otaczała kanały, przez które przepływały nośniki ładunku. Jednak mimo to przez lata technologia ta była zapomniana, przede wszystkim przez swoją złożoność. Produkcja GAAFET jest znacznie trudniejsza niż FinFET, problematyczne okazuje się precyzyjne formowanie nanorurek i ich dokładne otoczenie półprzewodnikowym materiałem. W dużym uproszczeniu przy starszych typach tranzystorów kolejne warstwy półprzewodnika mogą być nakładane w całości etapami, przy GAAFET jest to niemożliwe. Nakładana jest pojedyncza warstwa bramki z kanałem, później kolejna i kolejna, a problemem okazują się połączenia między warstwami tego samego typu.

Dlatego właśnie GAAFET, choć wdrażane są jeszcze na początku swojej drogi. Pierwszymi producentami, którzy ogłosili powszechne stosowanie tej technologii są Samsung i Intel (w nomenklaturze Intela GAAFET nazywane są RibbonFET). Tranzystory te pojawią się w 3nm procesie technologicznym tych firm, ale co ciekawe będące sporym graczem na rynku półprzewodników Tajwańskie TSMC ogłosiło, że nadal zamierza stosować FinFETy i dopiero przy przejściu na proces 2nm planowany na druga połowę 2025 roku firma przejdzie na GAAFET.

Implementacja GAAFET okazuje się trudna i problematyczna. Zdarzyło mi się czytać artykuły, w których podnoszona była teza, czy to, aby na pewno dobra droga i czy nie lepiej byłoby przejść od razu na „nanosheet” o czym za chwilę. Tranzystory GAAFET, mimo że wdrażane we współczesne procesy produkcyjne wydają się rozwiązaniem przejściowym. Eliminują one wady FinFET, ale przy okazji generują też swoje. Wspominałem już o trudnościach w produkcji, ale jest też kwestia przekroju samego kanału, który może okazać się zbyt mały, zwłaszcza w procesach mniejszych niż 2nm. Tym sposobem wracamy do punktu wyjścia zbyt małej przepustowości, ale tym razem konstrukcji GAAFET.

Nowe horyzonty – MBCFET

Niemal równolegle z procesem wdrażania tranzystorów GAAFET firma Samsung ogłosiła przygotowania do wdrożenia technologii MBCFET (obecnie nazwa ta została zastrzeżona przez Koreańczyków, dlatego wśród innych producentów możemy spodziewać się innego nazewnictwa). Jest to rozwinięcie technologii GAAFET z tą różnicą, że tym razem zamiast niewielkich kanałów w formie rurek zastosowano płaskie warstwy, tak zwane „nanosheet”. Osobiście nasuwają mi się skojarzenia z wielowarstwowymi płytkami PCB i ścieżkami umieszczonymi między poszczególnymi warstwami laminatu. Zastosowanie płaskich warstw pozwala zwiększyć przepustowość tranzystorów, jak i z najnowszych informacji wynika, że MBCFET są prostsze w produkcji. Same ścieżki również są elastyczniejsze pod względem konstrukcji, mogą one być szersze lub węższe, zależnie od mocy tranzystora.

Technologia MCBFET wydaje się obiecująca. Eliminuje ona problemy swoich poprzedników, oferując dodatkową elastyczność, której brakuje tranzystorom GAAFET. Jednak nadal jest to tylko prototyp i fakt, że dana firma obiecuje jakąś technologie, nie oznacza wcale, że ta stanie się światowym standardem. Jeśli ktoś nie wierzy, to polecam tutaj jeden z moich wcześniejszych artykułów o firmie Intel i jej perypetiach między innymi z procesem 14nm – „Intel, czyli lider, który nie nadąża”.

Czas pokaże, w jaką stronę wyewoluują krzemowe tranzystory. Wiadome jest jedno, zmiana jest potrzebna, jeśli chcemy zachować obecny rozwój technologiczny i nadal miniaturyzować układy scalone.

Źródła:

- https://www.anandtech.com/show/16041/where-are-my-gaafets-tsmc-to-stay-with-finfet-for-3nm

- https://www.youtube.com/watch?v=bfkIp_j0Iv8&t=32s

- https://rafalbartoszak.pl/sztuka-mikroelektroniki-krzemowe-uklady-scalone/

- https://www.ariat-tech.com/blog/the-basics-of-finfet-technology.html

- https://twojepc.pl/news40272/Intel-chce-produkowac-tranzystory-GAAFET-za-5-lat.html

- https://en.wikipedia.org/wiki/Multigate_device

- https://en.wikipedia.org/wiki/2_nm_process

- https://www.anandtech.com/show/17453/tsmc-unveils-n2-nanosheets-bring-significant-benefits

- https://resources.pcb.cadence.com/blog/2024-the-gaafet-fabrication-process

- https://news.samsungsemiconductor.com/global/samsung-begins-chip-production-using-3nm-process-technology-with-gaa-architecture/

- https://www.researchgate.net/publication/379259370_From_MOSFET_to_FinFET_to_GAAFET_The_evolution_challenges_and_future_prospects

Jak oceniasz ten wpis blogowy?

Kliknij gwiazdkę, aby go ocenić!

Średnia ocena: 5 / 5. Liczba głosów: 14

Jak dotąd brak głosów! Bądź pierwszą osobą, która oceni ten wpis.